Product Summary

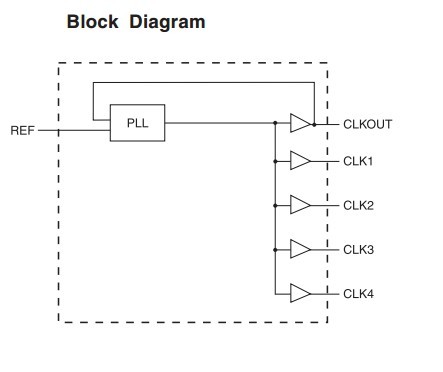

The ymif600-65 is a high performance, low skew, low jitter clock driver. It uses a phase lock loop (PLL) technology to align, in both phase and frequency, the REF input with the CLKOUT signal. It is designed to distribute high speed clocks in communication systems operating at speeds from 10 to 133 MHz. The ICS91305I comes in an eight pin 150 mil SOIC package. It has five output clocks. In the absence of REF input, will be in the power down mode. In this mode, the PLL is turned off and the output buffers are pulled low. Power down mode provides the lowest power consumption for a standby condition.

Parametrics

ymif600-65 absolute maximum ratings: (1)Supply Voltage: 7.0 V; (2)Logic Inputs (Except REF): GND –0.5 V to VDD + 0.5 V; (3)Logic Input REF: GND –0.5 V to GND + 5.5 V; (4)Ambient Operating Temperature: -40°C to +85°C; (5)Storage Temperature: –65°C to +150°C.

Features

ymif600-65 features: (1)Zero input - output delay; (2)Frequency range 10 - 133 MHz (3.3V); (3)5V tolerant input REF; (4)High loop filter bandwidth ideal for Spread Spectrum applications.; (5)Less than 200 ps Jitter between outputs; (6)Skew controlled outputs; (7)Skew less than 250 ps between outputs; (8)Available in 8 pin 150 mil SOIC & 173 mil TSSOP packages; (9)3.3V ±10% operation; (10)Supports industrial temperature range -40°C to 85°C.

Diagrams

(Hong Kong)

(Hong Kong)